# VT1802

## 120-CHANNEL SINGLE-ENDED, 60-CHANNEL DIFFERENTIAL +28 V / 73 V I/O CURRENT DRIVER

## USER'S MANUAL

P/N: 82-0106-000 Rev. February 13, 2007

VXI Technology, Inc.

2031 Main Street Irvine, CA 92614-6509 (949) 955-1894

## TABLE OF CONTENTS

| INTRODUCTION                                                            |    |

|-------------------------------------------------------------------------|----|

| Certification                                                           | 5  |

| Warranty                                                                | 5  |

| Limitation of Warranty                                                  | 5  |

| Restricted Rights Legend                                                | 5  |

| DECLARATION OF CONFORMITY                                               | 6  |

| Terms and Symbols                                                       |    |

| Warnings                                                                | 7  |

| SECTION 1                                                               | 11 |

| INTRODUCTION                                                            | 11 |

| Overview                                                                | 11 |

| VT1802 Specifications                                                   | 12 |

| SECTION 2                                                               | 13 |

| Preparation for Use                                                     | 13 |

| Introduction                                                            |    |

| Calculating System Power and Cooling Requirements                       |    |

| Setting the Chassis Backplane Jumpers                                   |    |

| Switch Settings                                                         |    |

| Setting the Logical Address                                             |    |

| Selecting the Extended Memory Space                                     |    |

| SECTION 3                                                               | 17 |

| MODULE USE AND OPERATION                                                | 17 |

| Overview                                                                |    |

| Backplane Interface                                                     |    |

| Modes of Operation                                                      |    |

| Trigger Operation                                                       |    |

| Calculating Hysteresis                                                  |    |

| Module Installation                                                     |    |

| Front Panel Connector Location Assignments                              | 21 |

| Section 4                                                               | 25 |

| Programming                                                             | 25 |

| Introduction                                                            |    |

| Addressing                                                              |    |

| Description of Registers - A16                                          |    |

| ID Register (0x00) — Read Only                                          |    |

| Logical Address Register (0x00) — Write Only                            |    |

| Device Type Register (0x02) — Read Only                                 |    |

| Status Register (0x04) — Read Only                                      | 27 |

| Control Register (0x04) — Write Only                                    | 27 |

| Offset Register (0x06) — Read & Write                                   | 27 |

| Reserved Register (0x08) — Read Only                                    |    |

| Reserved Register (0x0A) — Read Only                                    |    |

| Reserved Register (0x0C) — Read Only                                    |    |

| Version Number Register (0x0E) — Read Only                              |    |

| Interrupt Status Register (0x1A) — Read Only                            |    |

| Interrupt Control Register (0x1C) — Read & Write                        |    |

| Subclass Register (0x1E) — Read Only                                    | 29 |

| LED Control - NVM Access Register (0x20) — Read Only                    |    |

| LED Control - NVM Access Register (0x20) — Write Only                   |    |

| Output Control Function Bank Setup Register (0x22, 0x24) — Read & Write |    |

| Command Trigger Control Register (0x26) — Read & Write                  |    |

| Trace RAM Restart High Register (0x28) — Read & Write                       | 31 |

|-----------------------------------------------------------------------------|----|

| Trace RAM Restart Low Register (0x2A) — Read & Write                        |    |

| Trace RAM End High Register (0x2C) — Read & Write                           |    |

| Trace RAM End Low Register (0x2E) — Read & Write                            | 31 |

| Trace RAM Start Address HIGH Register (0x30) — Read & Write                 | 31 |

| Trace RAM Start Address LOW Register (0x32) — Read & Write                  |    |

| Trace Advance Trigger Select Register (0x34) — Write Only                   | 31 |

| Over-current Trigger Select & Power Enable Register (0x36) — Read-Write     | 32 |

| TTL Trigger Polarity Register (0x38) — Write Only                           | 32 |

| Trace RAM Control Register (0x3A) — Read & Write                            | 33 |

| Reserved Registers (0x3C) — Read & Write                                    | 33 |

| Trigger Advance Register (0x3E) — Write Only                                |    |

| Description of VT1802 Module Registers - A24 / A32 - Extended Memory        | 34 |

| Section 1 - Channel Output Enable Register — Read & Write                   | 34 |

| Section 1 - Channel Output Level Select Register — Read & Write             | 34 |

| Section 1 - Channel Over-current Status LO Register — Read Only             | 35 |

| Section 1 - Channel Over-current Status HI Register — Read Only             | 35 |

| Section 1 - Voltage Level Control Register — Read & Write                   | 36 |

| Section 1 - Channel Output Hardware Revision Register — Read Only           | 36 |

| Section 1 - Channel Monitor Output Status Register — Read Only              |    |

| Section 1 - Channel Monitor Output Threshold Voltage Register— Read & Write | 37 |

| Section 1 - Channel Monitor Hardware Revision Register — Read Only          | 38 |

| Section 2 - Channel Output Enable Register — Read & Write                   |    |

| Section 2 - Channel Output Level Select Register — Read & Write             |    |

| Section 2 - Channel Over-current Status LO Register — Read Only             |    |

| Section 2 - Channel Over-current Status HI Register — Read Only             |    |

| Section 2 - Voltage Level Control Register — Read & Write                   |    |

| Section 2 - Channel Output Hardware Revision Register — Read Only           |    |

| Section 2 - Channel Monitor Output Status Register — Read Only              | 41 |

| Section 2 - Channel Monitor Output Threshold Voltage Register— Read & Write |    |

| Section 2 - Channel Monitor Hardware Revision Register — Read Only          | 41 |

| Using the Code                                                              |    |

| Wrap Around Test Example                                                    | 42 |

| INDEX                                                                       | 47 |

|                                                                             |    |

#### **CERTIFICATION**

VXI Technology, Inc. (VTI) certifies that this product met its published specifications at the time of shipment from the factory. VTI further certifies that its calibration measurements are traceable to the United States National Institute of Standards and Technology (formerly National Bureau of Standards), to the extent allowed by that organization's calibration facility and to the calibration facilities of other International Standards Organization members.

#### WARRANTY

The product referred to herein is warranted against defects in material and workmanship for a period of three years from the receipt date of the product at customer's facility. The sole and exclusive remedy for breach of any warranty concerning these goods shall be repair or replacement of defective parts, or a refund of the purchase price, to be determined at the option of VTI.

For warranty service or repair, this product must be returned to a VXI Technology authorized service center. The product shall be shipped prepaid to VTI and VTI shall prepay all returns of the product to the buyer. However, the buyer shall pay all shipping charges, duties, and taxes for products returned to VTI from another country.

VTI warrants that its software and firmware designated by VTI for use with a product will execute its programming when properly installed on that product. VTI does not however warrant that the operation of the product, or software, or firmware will be uninterrupted or error free.

#### LIMITATION OF WARRANTY

The warranty shall not apply to defects resulting from improper or inadequate maintenance by the buyer, buyer-supplied products or interfacing, unauthorized modification or misuse, operation outside the environmental specifications for the product, or improper site preparation or maintenance.

VXI Technology, Inc. shall not be liable for injury to property other than the goods themselves. Other than the limited warranty stated above, VXI Technology, Inc. makes no other warranties, express or implied, with respect to the quality of product beyond the description of the goods on the face of the contract. VTI specifically disclaims the implied warranties of merchantability and fitness for a particular purpose.

#### RESTRICTED RIGHTS LEGEND

Use, duplication, or disclosure by the Government is subject to restrictions as set forth in subdivision (b)(3)(ii) of the Rights in Technical Data and Computer Software clause in DFARS 252.227-7013.

VXI Technology, Inc. 2031 Main Street Irvine, CA 92614-6509 U.S.A.

### DECLARATION OF CONFORMITY

Declaration of Conformity According to ISO/IEC Guide 22 and EN 45014

MANUFACTURER'S NAME VXI Technology, Inc.

MANUFACTURER'S ADDRESS 2031 Main Street

Irvine, California 92614-6509

**PRODUCT NAME** 120 single-ended, 60 differential channel current driver

MODEL NUMBER(S) VT1802

PRODUCT OPTIONS All

PRODUCT CONFIGURATIONS All

VXI Technology, Inc. declares that the aforementioned products conform to the requirements of the Low Voltage Directive 73/23/EEC and the EMC Directive 89/366/EEC (inclusive 93/68/EEC) and carries the "CE" mark accordingly. The products have been designed and manufactured according to the following specifications:

**SAFETY** EN61010 (2001)

EMC EN61326 (1997 w/A1:98) Class A

CISPR 22 (1997) Class A VCCI (April 2000) Class A

ICES-003 Class A (ANSI C63.4 1992) AS/NZS 3548 (w/A1 & A2:97) Class A

FCC Part 15 Subpart B Class A

EN 61010-1:2001

The products were installed into a C-size VXI mainframe chassis and tested in a typical configuration.

I hereby declare that the aforementioned products have been designed to comply with the relevant sections of the specifications listed above as well as complying with all essential requirements of the Low Voltage Directive.

February 2007

Steve Mauga, QA Manager

### **GENERAL SAFETY INSTRUCTIONS**

Review the following safety precautions to avoid bodily injury and/or damage to the product. These precautions must be observed during all phases of operation or service of this product. Failure to comply with these precautions or with specific warnings elsewhere in this manual violates safety standards of design, manufacture, and intended use of the product.

Service should only be performed by qualified personnel.

#### TERMS AND SYMBOLS

These terms may appear in this manual:

**WARNING** Indicates that a procedure or condition may cause bodily injury or death.

**CAUTION** Indicates that a procedure or condition could possibly cause damage to

equipment or loss of data.

These symbols may appear on the product:

**ATTENTION** - Important safety instructions

Frame or chassis ground

Indicates that the product was manufactured after August 13, 2005. This mark is placed in accordance with EN 50419, Marking of electrical and electronic equipment in accordance with Article 11(2) of Directive 2002/96/EC (WEEE). End-of-life product can be returned to VTI by obtaining an RMA number. Fees for take-back and recycling will apply if not prohibited by national law.

#### WARNINGS

Follow these precautions to avoid injury or damage to the product:

**Use Proper Power Cord**To avoid hazard, only use the power cord specified for this product.

**Use Proper Power Source** To avoid electrical overload, electric shock or fire hazard, do not use a power source that applies other than the specified voltage.

Use Proper Fuse To avoid fire hazard, only use the type and rating fuse specified for

this product.

#### WARNINGS (CONT.)

#### **Avoid Electric Shock**

To avoid electric shock or fire hazard, do not operate this product with the covers removed. Do not connect or disconnect any cable, probes, test leads, etc. while they are connected to a voltage source. Remove all power and unplug unit before performing any service. Service should only be performed by qualified personnel.

#### **Ground the Product**

This product is grounded through the grounding conductor of the power cord. To avoid electric shock, the grounding conductor must be connected to earth ground.

#### **Operating Conditions**

To avoid injury, electric shock or fire hazard:

- Do not operate in wet or damp conditions.

- Do not operate in an explosive atmosphere.

- Operate or store only in specified temperature range.

- Provide proper clearance for product ventilation to prevent overheating.

- DO NOT operate if any damage to this product is suspected.

Product should be inspected or serviced only by qualified personnel.

#### **Improper Use**

The operator of this instrument is advised that if the equipment is used in a manner not specified in this manual, the protection provided by the equipment may be impaired. Conformity is checked by inspection.

## **SUPPORT RESOURCES**

Support resources for this product are available on the Internet and at VXI Technology customer support centers.

#### VXI Technology World Headquarters

VXI Technology, Inc. 2031 Main Street Irvine, CA 92614-6509

Phone: (949) 955-1894 Fax: (949) 955-3041

#### VXI Technology Cleveland Instrument Division

5425 Warner Road Suite 13 Valley View, OH 44125

Phone: (216) 447-8950 Fax: (216) 447-8951

#### VXI Technology Lake Stevens Instrument Division

VXI Technology, Inc. 1924 - 203 Bickford Snohomish, WA 98290

Phone: (425) 212-2285 Fax: (425) 212-2289

#### **Technical Support**

Phone: (949) 955-1894 Fax: (949) 955-3041

E-mail: support@vxitech.com

Visit http://www.vxitech.com for worldwide support sites and service plan information.

VXI Technology, Inc.

## **SECTION 1**

## **INTRODUCTION**

#### **OVERVIEW**

The VT1802 is a high-performance high voltage I/O module with ten groups of 12 channels for a total of 120 channels per module. Each group of channels may be configured as an input or output under program control. Individual channels can be set to tri-state mode. In the output mode, each group can be configured with either 28 V or 73 V levels. Logic programmability (high/low) is on a per channel basis. Two level sensitive trigger inputs provide the flexibility to set external input conditions that must be met before a channel is enabled.

The VT1802 is an ideal module for multiple channel I/O applications which require the capability to source up to 140 mA per channel. Each channel has built-in over-current protection ensuring that the board will not be damaged if its specifications are exceeded.

VT1802 Introduction

#### VT1802 SPECIFICATIONS

| REQUIREMENTS                       |                                                        |  |  |  |  |

|------------------------------------|--------------------------------------------------------|--|--|--|--|

| CHANNELS                           |                                                        |  |  |  |  |

|                                    | 120 single-ended, 60 differential                      |  |  |  |  |

| VOLTAGE LEVELS                     |                                                        |  |  |  |  |

| 28 V (dc)                          | 0 V or +28 V (±1.0 V)                                  |  |  |  |  |

| 73 V (dc)                          | $2.5 \text{ V or } +73 \text{ V } (\pm 1.0 \text{ V})$ |  |  |  |  |

| CURRENT <sup>1</sup>               |                                                        |  |  |  |  |

| 28 V (dc)                          | 140 mA maximum                                         |  |  |  |  |

| 73 V (dc)                          | 1.0 mA maximum                                         |  |  |  |  |

| MAXIMUM LOAD <sup>2</sup>          |                                                        |  |  |  |  |

| @ 28 V (dc), 140 mA                | 84 channels, and                                       |  |  |  |  |

| @ 73 V (dc), 1 mA                  | 24 channels                                            |  |  |  |  |

| RISE/FALL TIME                     |                                                        |  |  |  |  |

| 28 V (dc)                          | <1 ms                                                  |  |  |  |  |

| 73 V (dc)                          | <2 ms                                                  |  |  |  |  |

| TRIGGER INPUTS                     |                                                        |  |  |  |  |

| External Triggers <sup>3,4,5</sup> | Two simultaneous TTL                                   |  |  |  |  |

| High State                         | 2.4 V minimum. Cannot exceed 5 V.                      |  |  |  |  |

| Low State                          | 0.4 V maximum. Must be greater than 0 V.               |  |  |  |  |

| Internal Triggers                  | Eight VXI backplane TTL triggers                       |  |  |  |  |

| Software Triggers                  | Via the soft front panel                               |  |  |  |  |

| LOGIC PROGRAMMABILITY              |                                                        |  |  |  |  |

|                                    | individual channel                                     |  |  |  |  |

| AMPLITUDE PROGRAMMAB               | ILITY                                                  |  |  |  |  |

|                                    | 12 channels/group                                      |  |  |  |  |

| CONNECTOR TYPES                    |                                                        |  |  |  |  |

| <b>Current Driver</b>              | 160-pin connector                                      |  |  |  |  |

| Power                              | 2-pin D-sub connector                                  |  |  |  |  |

| COOLING                            |                                                        |  |  |  |  |

| Worst Case                         | 150 W                                                  |  |  |  |  |

| Tri-State                          |                                                        |  |  |  |  |

|                                    | Per channel                                            |  |  |  |  |

| OVER-CURRENT PROTECTION            |                                                        |  |  |  |  |

|                                    | Per channel                                            |  |  |  |  |

|                                    |                                                        |  |  |  |  |

#### NOTE

- 1) External power supply required.

- 2) Assumes worst case air flow (i.e. 6-slot chassis with all slots open). The temperature rise is 6 °C less in a 13-slot chassis. Temperature rise can be lowered significantly if unused slots are covered.

- 3) If the external trigger experiences a voltage between 0.4 V and 2.4 V, the VT1802 may enter an indeterminate state. Measures should be taken to ensure that these conditions do not occur.

- 4) The external triggers are active-high level triggers that should be driven by a 5 V TTL signal. The signal must be free of glitches and stay in the high or low state for a minimum of 200 ns.

- 5) If the VT1802 external trigger experiences a voltage of greater than 6 V, damage will occur to the VT1802.

VT1802 Introduction

## **SECTION 2**

## PREPARATION FOR USE

#### Introduction

When the VT1802 is unpacked from its shipping carton, the contents should include the following items:

- (1) VT1802 module

- (1) VT1802 User's Manual (this manual)

All components should be immediately inspected for damage upon receipt of the unit.

The chassis should be checked to ensure that it is capable of providing adequate power and cooling for the VT1802. Once the chassis is found adequate, the VT1802's logical addresses and the backplane jumpers of the chassis should be configured prior to the VT1802's installation. After the VT1802 is assessed to be in good condition, it may be installed into an appropriate C-size or D-size VXIbus chassis in any slot other than slot zero.

#### CALCULATING SYSTEM POWER AND COOLING REQUIREMENTS

It is imperative that the chassis provide adequate power and cooling for this module. Referring to the chassis operation manual, confirm that the power budget for the system (the chassis and all modules installed therein) is not exceeded and that the cooling system can provide adequate airflow at the specified backpressure.

It should be noted that if the chassis cannot provide adequate power to the module, the instrument might not perform to specification or possibly not operate at all. In addition, if adequate cooling is not provided, the reliability of the instrument will be jeopardized and permanent damage may occur. Damage found to have occurred due to inadequate cooling could also void the warranty of the module.

#### SETTING THE CHASSIS BACKPLANE JUMPERS

Please refer to the chassis operation manual for further details on setting the backplane jumpers.

#### **SWITCH SETTINGS**

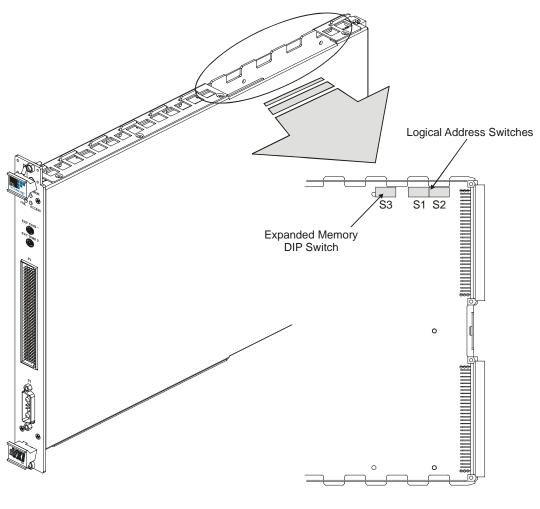

The VT1802 has three configurable switches, all located at the top of the unit near the rear connectors. The two rotary dials (S1 and S2) located closest to the rear of the interface card set the logical address (LA) for the module, while the two-position DIP switch (S3) sets the extended memory space for the module to either A24 or A32. Figure 1-1 below shows the location of these switches and the following paragraphs explain how they are configured.

Rear of Module

FIGURE 1-1: SWITCH LOCATIONS

#### Setting the Logical Address

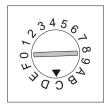

The LA of the VT1802 is set by two rotary switches with each switch labeled with positions 0 through F. S1, the switch closer to the front panel of the module, is the least significant bit (**LS** or "**Front**"), and S2, the switch located towards the back of the module, is the most significant bit (**MS** or "**Back**"). To set the LA, simply rotate the pointer to the desired value. For example, to set the LA to 25, first convert the decimal number to the hexadecimal value of 19. Next, set the back switch to 1 and the front switch to 9. See Figure 1-2. Here are a couple of conversion examples:

| Example | 1 |

|---------|---|

| Example | 1 |

| LA<br>(decimal) | Divide<br>by 16 |   | MS   | LS             |                                                                             |

|-----------------|-----------------|---|------|----------------|-----------------------------------------------------------------------------|

| 25              | 25 / 16         | = | 1    | w/ 9 remaining | Divide the decimal value by 16 to get the MS and the LS.                    |

|                 |                 | = | 0001 | 1001           | The 1 is the MS, and the remainder of 9 is the LS.                          |

|                 |                 | = | 1    | 9              | Convert to hexadecimal. Set the back switch to 1 and the front switch to 9. |

#### **BACK**

#### **FRONT**

FIGURE 1-2: LOGICAL ADDRESS EXAMPLE 1

Here is another way of looking at the conversion: LA = (back switch x 16) + front switch

$LA = (1 \times 16) + 9$ LA = 16 + 9

LA = 25

#### Example 2

| LA<br>(decimal) | Divide<br>by 16 |   | MS   | LS            |                                                                             |

|-----------------|-----------------|---|------|---------------|-----------------------------------------------------------------------------|

| 200             | 200 / 16        | = | 12   | w/8 remaining | Divide by 16.                                                               |

|                 |                 | = | 1100 | 1000          | Convert to MS and LS.                                                       |

|                 |                 | = | C    | 8             | Convert to hexadecimal. Set the back switch to C and the front switch to 8. |

#### **FRONT**

FIGURE 1-3: LOGICAL ADDRESS EXAMPLE 2

Set the address switches to  $\mathbf{FF}$  (factory default) for dynamic configuration. Upon power-up, the resource manager will assign a logical address. See "Section F - Dynamic Configuration" in the  $VXIbus\ Specification$  for further information.

There is only one logical address per VT1802 base unit. Address assignments for individual modules are handled through the A24/A32 address space allocation (see *Description of VT1802 Module Registers - A24 / A32 - Extended Memory* for more information).

#### Selecting the Extended Memory Space

The extended memory space of VT1802 base units is set by a DIP switch that is located on the top edge of the interface card (see Figure 1-1). Position 1, located to the left on the DIP switch, selects between A24 and A32 memory address space. In the UP position, the VT1802 will request A24 space. In the DOWN position (factory default), the VT1802 will request A32 space. (Position 2 is not currently used.) The selection of the address space should be based upon the memory allocation requirements of the system that the VT1802 module will be installed. The amount of memory allocated to a VT1802 module is independent of the address space selected.

#### NOTE

GPIB slot 0 controllers will not support the VT1802 as configured from the factory as they do not support dynamically configured logical addresses or A32 address space. The VT1802 can be reconfigured to support GPIB slot 0s by setting the logical address switches to a static address and having the address space configured for A24. If using a slot 0 controller that supports A32 extended memory space, it is recommended that the switches be left in their factory configured state to take advantage of the greater available address space capacity.

## **SECTION 3**

### MODULE USE AND OPERATION

#### **OVERVIEW**

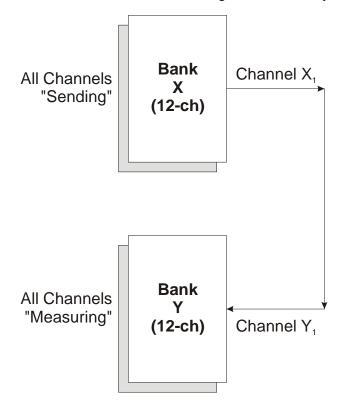

The VT1802 is a current driver module, providing 10 banks of 12 channels (120 channels) from two constant voltage sources. Each bank of twelve channels may be configured as a current source or a current sink of different voltages under software program control. The channels can be used in either single-ended of differential mode.

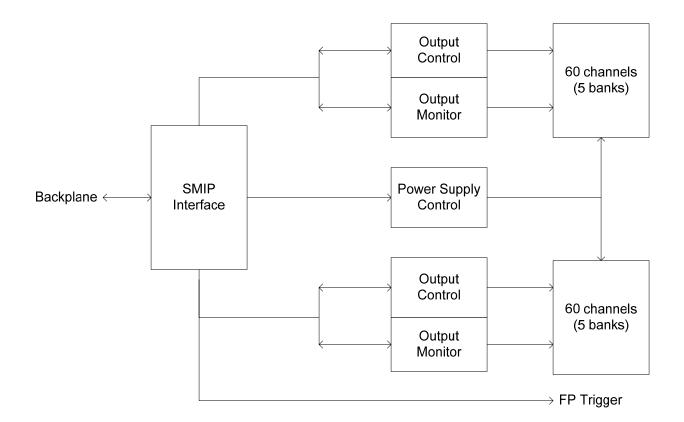

The VT1802 contains two identical sections with five banks (60 channels) a piece. The control functions divided into three sections:

#### Backplane Interface

Output Control Enable Channel Output

Select Channel Level Select Bank Voltage Over-current Status

Output Monitor Output Threshold Voltage

Channel Output Level Status (Readback)

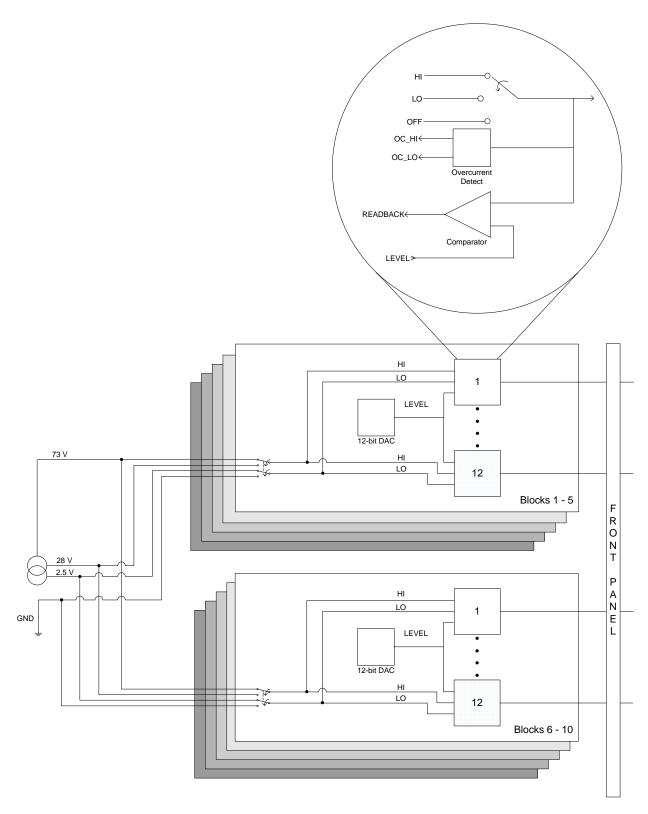

See Figure 2-1 illustrates these divisions.

FIGURE 2-1: BASIC OPERATION DIAGRAM

Each section is further divided into five 12 channel banks (see Figure 2-2). Each bank of 12 channels is set to either 73 V (HI) and 2.5 V (LO) or 28 V (HI) and GND (LO). Each individual channel can be set to either HI, LO, or OFF. If a user, for example, sets bank 2 to 73 V, then channels 13 – 24 can be either 73 V, 2.5 V, or off. Similarly, if the user sets bank 6 to 28 V, then channels 61 – 72 can be either 28 V, GND, or off. Each channel is capable of sourcing/sinking up to 140 mA at 28 V. The maximum for the 73 V line is 1 mA. It is imperative to keep this in mind when operating the VT1802. Should an over-current condition (I > 140 mA) occur, the channel is shut off and an over-current event is registered for that channel. By accessing the ENABLE and LEVEL registers via the soft front panel, a channel can be set to ON/OFF or HI/LO, respectively. Each channel is additionally capable of Output Enable, Output Selection, and Output Level Readback.

NOTE

The 140 mA current capability should only be applied to the 28 V setting. If used in the 73 V setting, only ten channels can be used maximum. If more current is required, the power supply will lower to 28 V.

FIGURE 2-2: VT1802 BLOCK DIAGRAM

#### MODES OF OPERATION

Two different modes of operation are available on the VT1802. These modes are described below.

| Mode                | Explanation                                                                                                                                                                      | Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Single-ended        | The channel can be configured to source current to or sink current from an external source                                                                                       | If a bank is set to 73 V/28 V, the channel will source up to 1 mA/140 mA (controlled by load).  If a bank is set to 2.5 V/GND, the channel will sink up to 1 mA/140 mA (controlled by load)                                                                                                                                                                                                                                                                                                                                                |

| Differential        | Two channels of the same voltage are used, but set to different levels (73 V to 2.5 V or 28 V to GND) where one is used as the current source and one is used as a current sink. | If bank 2 is set to 28 V and GND, then channel 13 can be 28 V and connected to channel 24 (set at GND) via a proper load, or  Bank 7 can be set to 73 V and 2.5 V, then channel 73 can be 73 V and connected to channel 84 (set at 2.5 V) via a proper load, or  All channels from bank x set at either 28 V/73 V and connected to all channels from bank Y set at either GND/2.5 V.  It is recommended that the latter example be used in practice for ease of use and to reduce the likelihood of making an incorrect wiring connection. |

| Note: the user must | provide the appropriate load to avoid of                                                                                                                                         | over-current.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

#### TRIGGER OPERATION

The VT1802 can be controlled via software. The user can issue commands to execute several functions: select channel, level, Select Bank Voltage, Over-current Status, etc. Two operations, Channel Output Enable and Channel Output Level Select, are used to engage the VT1802 when entered or via triggers supplied by any of the three following sources:

- 1) **External Trigger**: the VT1802 has two front panel connectors. They allow for 5 V TTL-level triggering and OR or AND operation can be selected.

- 2) **Backplane TTL0-7 Trigger**: There are eight backplane TTL trigger signals. These triggers are edge triggering and can be selected falling or rising edge triggering.

- 3) Software Trigger.

## WARNINGS

- 1) If the external trigger experiences a voltage between 0.4 V and 2.4 V, the VT1802 may enter an indeterminate state. Measures should be taken to ensure that these conditions do not occur.

- 2) The external triggers are active-high level triggers that should be driven by a 5 V TTL signal. The signal must be free of glitches and stay in the high or low state for a minimum of 200 ns.

- 3) If the VT1802 external trigger experiences a voltage of greater than 6 V, damage will occur to the VT1802.

The priority of triggering is as following: EXT TRIGGERS, BACKPLANE TTL0-7 Trigger, Software Trigger. If all or many triggers are enabled, the highest priority will take precedent. The rest will be ignored.

In a trigger mode, the user first must set up the desired triggers by accessing the Command Trigger Control Register (see page 30). When the VT1802 is already in the trigger mode, any change to the Channel Output Enable and Channel Output Level Select will not be executed until:

- 1) Both EXT TRIG1 and EXT TRIG2 go to a TTL-high level (for AND setting), or

- 2) Either EXT TRIG1 or EXT TRIG2 goes to a TTL-high level (for OR setting), or

- 3) Any falling/rising edge on Backplane TTL0-7 Triggers line (for TTL Trigger setting and External Trigger is not enabled), or

- 4) Software trigger bit in the Trigger Control Register is set.

All other functions are not affected by triggering.

Channel output can be monitored via a comparator and a read-back register. The level of the comparator is set in a DAC in each bank. The DAC setting must take hysteresis and component variation into account.

#### **CALCULATING HYSTERESIS**

The following equation is used to calculate hysteresis for the VT1802:

=

$$Vut = (20/21) \mathbf{V} \times Vdac + (75/21) \mathbf{V}$$

$Vlt = (20/21) \mathbf{V} \times Vdac$

where:

Vut = upper threshold limit Vlt = lower threshold limit Vdac is the output of the DAC set by the user (LEVEL) Vdac range = 0 V - 75 V Vdac resolution = 75/4095 = 18.3 mV

Component variation error is  $\pm 3\%$  for Vdac, hence, Vut and Vlt have a  $\pm 3\%$  error as well. The hysteresis voltage is 3.6 V for the whole range

Please note that, due to hysteresis, as Vdac is set to 0, the upper limit threshold, Vut, will be 3.6 V

#### MODULE INSTALLATION

Before installing a VT1802 module, make sure that the mainframe is powered down. Insert the module into the chassis by orienting the module so that the card guides of the module can be inserted into the slot of the chassis. Position the module so that it fits into the chassis slot groove. Once the module is properly aligned, push the module back and firmly insert it into the backplane connector.

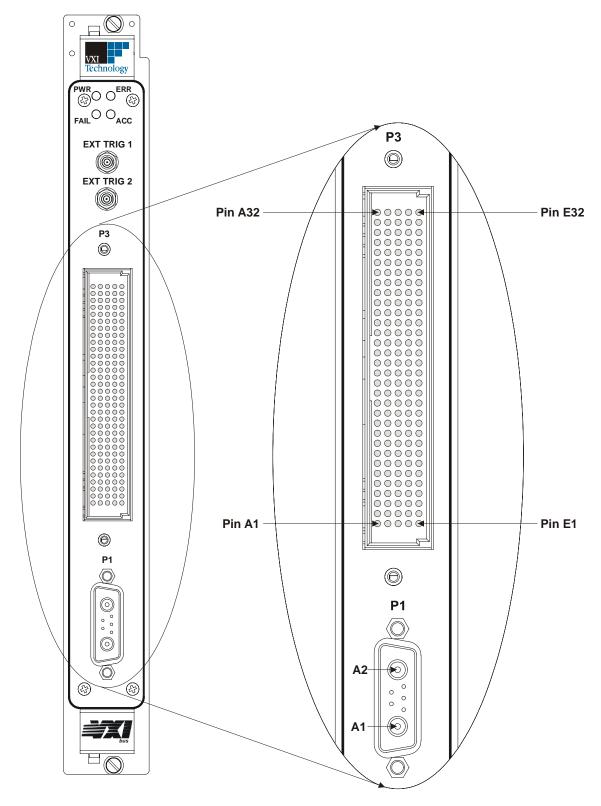

#### FRONT PANEL CONNECTOR LOCATION ASSIGNMENTS

The Figure 2-3 illustrates the physical location assignments for each connector on the front panel of the module. This view depicts all connectors for both the VT1802.

The module's front panel LEDs may be monitored for an indication the VXI module's operation. The function of the LEDs is as follows:

| LED Name | Function                                                                |  |  |

|----------|-------------------------------------------------------------------------|--|--|

| Power    | Illuminates green when power is applied to the module.                  |  |  |

|          | Not illuminated when there is no power to the chassis.                  |  |  |

|          | This LED is not programmable.                                           |  |  |

| Error    | Not illuminated under normal operating conditions.                      |  |  |

|          | Illuminates red if an Error condition occurs.                           |  |  |

|          | This LED is programmable.                                               |  |  |

| Fail     | Illuminates green under normal operating conditions.                    |  |  |

|          | Illuminates red if an ac fail condition occurs.                         |  |  |

|          | This LED is programmable.                                               |  |  |

| Access   | This LED flashes green when data is accesses or written to the VT1802's |  |  |

|          | registers.                                                              |  |  |

FIGURE 2-3: CONNECTOR LOCATION ASSIGNMENTS

TABLE 2-1: FRONT PANEL SIGNAL ASSIGNMENTS

| ROW A | SIGNAL | ROW B | SIGNAL | ROW C | SIGNAL | ROW D | SIGNAL | ROW E | SIGNAL |

|-------|--------|-------|--------|-------|--------|-------|--------|-------|--------|

| 1     | CHN116 | 1     | CHN117 | 1     | CHN118 | 1     | CHN119 | 1     | CHN120 |

| 2     | CHN111 | 2     | CHN112 | 2     | CHN113 | 2     | CHN114 | 2     | CHN115 |

| 3     | CHN106 | 3     | CHN107 | 3     | CHN108 | 3     | CHN109 | 3     | CHN110 |

| 4     | GND    |

| 5     | CHN101 | 5     | CHN102 | 5     | CHN103 | 5     | CHN104 | 5     | CHN105 |

| 6     | CHN96  | 6     | CHN97  | 6     | CHN98  | 6     | CHN99  | 6     | CHN100 |

| 7     | CHN91  | 7     | CHN92  | 7     | CHN93  | 7     | CHN94  | 7     | CHN95  |

| 8     | GND    |

| 9     | CHN56  | 9     | CHN57  | 9     | CHN58  | 9     | CHN59  | 9     | CHN60  |

| 10    | CHN51  | 10    | CHN52  | 10    | CHN53  | 10    | CHN54  | 10    | CHN55  |

| 11    | CHN46  | 11    | CHN47  | 11    | CHN48  | 11    | CHN49  | 11    | CHN50  |

| 12    | GND    |

| 13    | CHN41  | 13    | CHN42  | 13    | CHN43  | 13    | CHN44  | 13    | CHN45  |

| 14    | CHN36  | 14    | CHN37  | 14    | CHN38  | 14    | CHN39  | 14    | CHN40  |

| 15    | CHN31  | 15    | CHN32  | 15    | CHN33  | 15    | CHN34  | 15    | CHN35  |

| 16    | GND    |

| 17    | GND    |

| 18    | CHN26  | 18    | CHN27  | 18    | CHN28  | 18    | CHN29  | 18    | CHN30  |

| 19    | CHN21  | 19    | CHN22  | 19    | CHN23  | 19    | CHN24  | 19    | CHN25  |

| 20    | CHN16  | 20    | CHN17  | 20    | CHN18  | 20    | CHN19  | 20    | CHN20  |

| 21    | GND    |

| 22    | CHN11  | 22    | CHN12  | 22    | CHN13  | 22    | CHN14  | 22    | CHN15  |

| 23    | CHN6   | 23    | CHN7   | 23    | CHN8   | 23    | CHN9   | 23    | CHN10  |

| 24    | CHN1   | 24    | CHN2   | 24    | CHN3   | 24    | CHN4   | 24    | CHN5   |

| 25    | GND    |

| 26    | CHN86  | 26    | CHN87  | 26    | CHN88  | 26    | CHN89  | 26    | CHN90  |

| 27    | CHN81  | 27    | CHN82  | 27    | CHN83  | 27    | CHN84  | 27    | CHN85  |

| 28    | CHN76  | 28    | CHN77  | 28    | CHN78  | 28    | CHN79  | 28    | CHN80  |

| 29    | GND    |

| 30    | CHN71  | 30    | CHN72  | 30    | CHN73  | 30    | CHN74  | 30    | CHN75  |

| 31    | CHN66  | 31    | CHN67  | 31    | CHN68  | 31    | CHN69  | 31    | CHN70  |

| 32    | CHN61  | 32    | CHN62  | 32    | CHN63  | 32    | CHN64  | 32    | CHN65  |

#### NOTE

- 1) The 48 V input connector P1 is a 15-pin D-sub connector.

- 2) P1 is a D-sub connector with two pins, A1 and A2 for connection to power. A1 is +48 V and A2 is -48 V. IT IS IMPERATIVE THAT THE POLARITY OF THESE CONNECTORS NOT BE REVERSED AS IT WILL CAUSE DAMAGE TO INTERNAL CIRCUITRY. A mating connector and pins are provided with the unit.

VXI Technology, Inc.

## **SECTION 4**

### **PROGRAMMING**

#### Introduction

VT1802 modules are VXIbus register-based devices for high-speed data retrieval. Register-based programming is a series of **reads** and **writes** directly to the module's registers (this includes accesses to the modules RAM). This eliminates the time for command parsing thus increasing speed.

#### ADDRESSING

The VXI Technology switching modules utilize either the A24 or A32 space (set via the DIP switches on the bottom of the VT1802 module, see page 16) of the shared-memory architecture. To read or write to a module register, a register address needs to be specified. This is done by using the offset value (assigned by the resource manager) and multiplying it by 256 or 64 k to get the base address in A24 or A32 address space, respectively.

A24 Base Address = Offset value \* 0x0100 (or 256)

A32 Base Address = Offset value \* 0x10000 (or 65,536)

The A24 or A32 offset value, assigned by the resource manager, can also be accessed by reading the A16 Offset Register. To address the A16 Offset Register use the following formula:

A16 Base Address = (Logical Address \* 64) + 0xC000 (or 49,152)

then

A16 Offset Register Address = A16 Base Address + 6

See A16 Memory Map on page 26 and the A24/A32 address space allocation on page 34.

TABLE 3-1: VT1802 REGISTER MAP - A16

| OFFSET | WRITE FUNCTION                             | READ FUNCTION                      |

|--------|--------------------------------------------|------------------------------------|

| 0x3E   | Trace Advance                              | Reserved                           |

| 0x3C   | Reserved                                   | Reserved                           |

| 0x3A   | Trace RAM Control                          | Trace RAM Control                  |

| 0x38   | TTL Trigger Polarity                       | Reserved                           |

| 0x36   | Over-current Trigger Select & Power Enable | Reserved                           |

| 0x34   | Trace Advance Trigger Select               | Reserved                           |

| 0x32   | Trace RAM Start Address LOW                | Trace RAM Start Address LOW        |

| 0x30   | Trace RAM Start Address HIGH               | Trace RAM Start Address HIGH       |

| 0x2E   | Trace RAM End LOW                          | Trace RAM End LOW                  |

| 0x2C   | Trace RAM End HIGH                         | Trace RAM End HIGH                 |

| 0x2A   | Trace RAM Restart LOW                      | Trace RAM Restart LOW              |

| 0x28   | Trace RAM Restart HIGH                     | Trace RAM Restart HIGH             |

| 0x26   | Command Trigger Control                    | Command Trigger Control            |

| 0x24   | Output Control Function Bank Setup         | Output Control Function Bank Setup |

| 0x22   | Output Control Function Bank Setup         | Output Control Function Bank Setup |

| 0x20   | LED Control - NVM Access                   | LED Control - NVM Access           |

| 0x1E   | Reserved                                   | Subclass Register                  |

| 0x1C   | Interrupt Control                          | Interrupt Control                  |

| 0x1A   | Reserved                                   | Interrupt Status                   |

| 0x18   | Reserved                                   | Reserved                           |

| 0x16   | Reserved                                   | Reserved                           |

| 0x14   | Reserved                                   | Reserved                           |

| 0x12   | Reserved                                   | Reserved                           |

| 0x10   | Reserved                                   | Reserved                           |

| 0x0E   | Reserved                                   | Version Number                     |

| 0x0C   | Reserved                                   | Reserved                           |

| 0x0A   | Reserved                                   | Reserved                           |

| 0x08   | Reserved                                   | Reserved                           |

| 0x06   | Offset Register                            | Offset Register                    |

| 0x04   | Control Register                           | Status Register                    |

| 0x00   | Reserved                                   | Device Type Register               |

| 0x00   | LA Register                                | ID Register                        |

**NOTE** If the VXI*plug&play* drivers are being used, these registers normally do not need to be accessed.

### **DESCRIPTION OF REGISTERS - A16**

The following describes the registers shown in the VT1802 Register Map for A16 address space.

|           | ID Register (0x00) — Read Only |                                                        |  |  |

|-----------|--------------------------------|--------------------------------------------------------|--|--|

| D11 - D0  | Manufacturer's ID              | VXI Technology, Inc., set to F4B <sub>16</sub>         |  |  |

| D13 - D12 | Address Space                  | $A16/A24 = 00_2$<br>$A16/A32 = 01_2$                   |  |  |

| D15 - D14 | Device Class                   | Extended register based device, set to 01 <sub>2</sub> |  |  |

| Logical Address Register (0x00) — Write Only |                 |                                                                                                                                                                           |  |

|----------------------------------------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| D7 - D0                                      | Logical Address | Sets the new logical address in a dynamically configured module. When set for dynamic configuration (set to FF <sub>16</sub> ) a soft reset will not alter the configured |  |

|                                              |                 | logical address, while a hard reset will set the register back to FF <sub>16</sub> .                                                                                      |  |

| D15 - D8                                     | Reserved        | Writing to this range has no effect.                                                                                                                                      |  |

| Device Type Register (0x02) — Read Only |                 |                                        |  |

|-----------------------------------------|-----------------|----------------------------------------|--|

| D11 - D0                                | Model Code      | Model 296, set to 128 <sub>16</sub>    |  |

| D15 - D12                               | Required Memory | 2 MB, set to 2 <sub>16</sub> , for A24 |  |

|                                         |                 | 2 MB, set to A <sub>16</sub> , for A32 |  |

|          | Status Register (0x04) — Read Only |                                                                 |  |  |

|----------|------------------------------------|-----------------------------------------------------------------|--|--|

| D15      | A24/A32 Active                     | 1 = Indicates that A24/A32 memory space access is enabled       |  |  |

|          |                                    | 0 = Indicates that A24/A32 memory space access is locked out    |  |  |

| D14      | MODID*                             | 1 = Indicates that the module is not selected by the MODID line |  |  |

|          |                                    | 0 = Indicates that the module is selected by the MODID line.    |  |  |

| D13 - D4 | Reserved                           | These bits always read as 11,1111,1111 <sub>2</sub>             |  |  |

| D3       | Ready                              | This bit always reads as 1 <sub>2</sub>                         |  |  |

| D2       | Passed                             | This bit always reads as 1 <sub>2</sub>                         |  |  |

| D1 - D0  | Reserved                           | These bits always read as 11 <sub>2</sub>                       |  |  |

|          |                 | Control Register (0x04) — Write Only                                                                                                       |

|----------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| D15      | A24/A32 Enable  | 1 = Write a 1 to this bit to enable A24/A32 memory access                                                                                  |

|          |                 | 0 = To disable access                                                                                                                      |

| D14 – D2 | Reserved        | Writes to these bits have no effect.                                                                                                       |

| D1       | Sysfail Inhibit | Write a 1 to this bit to prevent the module from asserting the SYSFAIL* line.                                                              |

| D0       | Reset           | 1 = Write a 1 to this bit to force the registers on the VT1802 interface into a reset state 0 = Write a 0 to release this soft reset state |

|          |                 | Note: This does not reset output channels on the module.                                                                                   |

| Offset Register (0x06) — Read & Write |                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|---------------------------------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| D15 - D0                              | A24/A32 Memory<br>Offset | The value written to this 16-bit register multiplied by 256 sets the base address of the A24 memory space used by the module. The value written to this 16-bit register multiplied by 65,536 sets the base address of the A32 memory space used by the module. A read from this register reflects the previously written value. Because of the required memory size, bits D4-D0 are disregarded on writes and always read back as 0. Upon receiving a hard reset, all bits in this register are set to 0. A soft reset does not affect the value in this register. |  |

| Reserved Register (0x08) — Read Only |        |                                        |  |

|--------------------------------------|--------|----------------------------------------|--|

| D15 - D0                             | Unused | Always read back as FFFF <sub>16</sub> |  |

| Reserved Register (0x0A) — Read Only |        |                                        |  |

|--------------------------------------|--------|----------------------------------------|--|

| D15 - D0                             | Unused | Always read back as FFFF <sub>16</sub> |  |

| Reserved Register (0x0C) — Read Only |        |                                        |  |

|--------------------------------------|--------|----------------------------------------|--|

| D15 - D0                             | Unused | Always read back as FFFF <sub>16</sub> |  |

| Version Number Register (0x0E) — Read Only |                            |                                                                                                       |  |

|--------------------------------------------|----------------------------|-------------------------------------------------------------------------------------------------------|--|

| D15 - D8                                   | Firmware Version<br>Number | Not applicable, reads back as $00_{16}$                                                               |  |

| D7 - D0                                    | Hardware Version<br>Number | This code is incremented each time hardware changes are made to the VT1802 module VXI Interface FPGA. |  |

|           | Interrupt Status Register (0x1A) — Read Only |                                                                                 |  |

|-----------|----------------------------------------------|---------------------------------------------------------------------------------|--|

| D15       | Scan Function                                | The latest scan list update is complete.                                        |  |

|           | done                                         |                                                                                 |  |

| D14 - D10 | Unused                                       | These bits are always read back as 0's.                                         |  |

| D9        | Over-current Error                           | An Over-current event, either HI or LO, has occurred on a channel between       |  |

|           | Detected                                     | 61 and 120. The OC registers for this bank must be queried to identify the      |  |

|           | Channels 61 thru                             | channel(s) that indicated an Over-current Event.                                |  |

|           | 120                                          |                                                                                 |  |

|           |                                              | The Over-current event will reset the affected channel, effectively shutting it |  |

|           |                                              | off. To turn the channel on again its Select bit must be re-set. See the        |  |

|           |                                              | A24/A32 Channel Select Register definitions on page 34.                         |  |

| D8        | Over-current Error                           | An Over-current event, either HI or LO, has occurred on a channel between 1     |  |

|           | Detected                                     | and 60. The OC registers for this bank must be queried to identify the          |  |

|           | Channels 1 thru 60                           | channel/s that indicated an Over-current Event.                                 |  |

|           |                                              |                                                                                 |  |

|           |                                              | The Over-current event will reset the affected channel, effectively shutting it |  |

|           |                                              | off. To turn the channel on again its Select bit must be re-set. See the        |  |

|           |                                              | A24/A32 Channel Select Register definitions on page 34.                         |  |

| D7 - D0   | Reserved                                     | Always reads back as FFFF <sub>16</sub>                                         |  |

**Note**: This status register may be used in a polled fashion rather than allowing the events above to generate an Interrupt. A read of this register will clear any active bits. Bits that are not set or are about to be set are not affected by a read of this register.

|               | Interru                                                                                | ıpt Control Register (0x1C) — Read & Write                                                                                                                       |  |

|---------------|----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| D15           | Scan Function                                                                          | 0 = Enabled                                                                                                                                                      |  |

|               | done mask bit                                                                          | 1 = Disabled                                                                                                                                                     |  |

| D14 – D10     | Reserved                                                                               | Writes to these bits have no effect.                                                                                                                             |  |

| D9            | Over-current Error                                                                     | 0 = Enabled                                                                                                                                                      |  |

|               | Event                                                                                  | 1 = Disabled                                                                                                                                                     |  |

|               | Channels 61                                                                            |                                                                                                                                                                  |  |

|               | through 120                                                                            |                                                                                                                                                                  |  |

| D8            | Over-current Error                                                                     | 0 = Enabled                                                                                                                                                      |  |

|               | Event                                                                                  | 1 = Disabled                                                                                                                                                     |  |

|               | Channels 1 thru 60                                                                     |                                                                                                                                                                  |  |

| D7            | IR ENA*                                                                                | 0 = Writing a 0 to this bit enables interrupter capabilities                                                                                                     |  |

|               |                                                                                        | 1 = Writing a 1 to this bit disables interrupter capabilities                                                                                                    |  |

| D6            | IH ENA*                                                                                | The module has no interrupt handler capability; therefore writing a 1 or 0 has no effect. A 1 is always read back for this bit.                                  |  |

| D5 - D3       | Interrupter IRQ<br>Line                                                                | The complement of the value programmed into these three bits reflects the selected IRQ line used by the module. A value of 011 <sub>2</sub> would select IRQ4, a |  |

|               | Line                                                                                   | value of 000 <sub>2</sub> would select IRQ7, and a value of 111 <sub>2</sub> would disconnect the                                                                |  |

|               |                                                                                        | IRQ lines.                                                                                                                                                       |  |

| D2 - D0       | Handler IRQ Line                                                                       | The module has no interrupt handler capability; therefore writing to these                                                                                       |  |

|               |                                                                                        | bits has no effect. A 111 <sub>2</sub> is always read back for these bits.                                                                                       |  |

| Note that all | Note that all bits in this register are set to 1 upon receipt of a hard or soft reset. |                                                                                                                                                                  |  |

|          | Subclass Register (0x1E) — Read Only |                                      |  |

|----------|--------------------------------------|--------------------------------------|--|

| D15      | VXIbus Extended<br>Device            | Always reads as 1.                   |  |

| D14 - D0 | Extended Memory<br>Device            | Always reads as 7FFD <sub>16</sub> . |  |

| LED Control - NVM Access Register (0x20) — Read Only |                   |                                                                    |

|------------------------------------------------------|-------------------|--------------------------------------------------------------------|

| D15 – D9                                             | Unused            | All bits are always 1.                                             |

| D8                                                   | Error LED Control | Reads back the value of ERROR LED.                                 |

| D7 - D1                                              | Unused            | All bits are always 1.                                             |

| D0                                                   |                   | Reads back the serial data stream from the on board EEPROM device. |

| LED Control - NVM Access Register (0x20) — Write Only |                   |                                                                |

|-------------------------------------------------------|-------------------|----------------------------------------------------------------|

| D15 – D9                                              | Unused            | Data written to these bits have no effect.                     |

| D8                                                    | Error LED Control | 1 = Write a 1 to this bit to enable the front panel ERROR LED  |

|                                                       |                   | 0 = Write a 0 to this bit to disable the front panel ERROR LED |

| D7-D2                                                 | Unused            | Data written to these bits have no effect.                     |

| D1                                                    |                   | Serial clock for module; should be a logic 1 when not used.    |

| D0                                                    |                   | Serial data input; must be a logic 1 when not used.            |

|          | Output Control Function Bank Setup Register (0x22, 0x24) — Read & Write |                                                                        |

|----------|-------------------------------------------------------------------------|------------------------------------------------------------------------|

| D15 - D8 |                                                                         | Always write 0x00.                                                     |

| D7 - D0  |                                                                         | Register 0x22 sets the banks starting from Bank1 to Bank5 for Channel  |

|          |                                                                         | Output Control Function on Motherboard.                                |

|          |                                                                         | Register 0x24 sets the banks starting from Bank6 to Bank10 for Channel |

|          |                                                                         | Output Control Function on Daughterboard.                              |

|          |                                                                         | Used in Trace Mode ONLY.                                               |

|      | Command Trigger Control Register (0x26) — Read & Write |                                                                                                            |  |

|------|--------------------------------------------------------|------------------------------------------------------------------------------------------------------------|--|

| D15  | External Trigger 1                                     | 1 = Write a 1 to this bit to enable External Trigger 1 to control the transfer                             |  |

|      | Enable                                                 | of data from the input buffer to the output buffer.                                                        |  |

|      |                                                        | 0 = Write a 0 to disable this trigger                                                                      |  |

|      |                                                        | $P_{\text{on}}$ state = 0                                                                                  |  |

| D14  | External Trigger 2                                     | 1 = Write a 1 to this bit to enable External Trigger 2 to control the transfer                             |  |

|      | Enable                                                 | of data from the input buffer to the output buffer.                                                        |  |

|      |                                                        | 0 = Write a 0 to disable this trigger                                                                      |  |

| D13  | Doolmlana                                              | $P_{on}$ state = 0<br>1 = Write a 1 to this bit to enable the VT1802 to execute user command if            |  |

| D13  | Backplane<br>TTL0-7 Trigger                            | any bit TTLTRIG0-7 change edge as defined below.                                                           |  |

|      | 11L0-/ Illigger                                        | 0 = Write a 0 to disable this trigger                                                                      |  |

|      |                                                        | $P_{\text{on}}$ state = 0                                                                                  |  |

| D12  | Software Trigger                                       | 1 = Write a 1 to this bit to enable the VT1802 to execute user command if                                  |  |

| 512  | Enable                                                 | Software Trigger (bit D9) is set                                                                           |  |

|      |                                                        | 0 = Write a 0 to disable this trigger                                                                      |  |

|      |                                                        | $P_{on}$ state = 1                                                                                         |  |

| D11  | External Trig                                          | 1 = Write a 1 to this bit set the external triggers to: EXT TRIG1 AND EXT                                  |  |

|      | Control                                                | TRIG2                                                                                                      |  |

|      |                                                        | 0 = Write a 0 to this bit set the external triggers to: EXT TRIG1 OR EXT                                   |  |

|      |                                                        | TRIG2                                                                                                      |  |

|      |                                                        | $P_{on}$ state = 0                                                                                         |  |

|      |                                                        |                                                                                                            |  |

|      |                                                        | For this bit's operation to be properly executed, both EXT TRIG1 and EXT                                   |  |

| D10  | TTL Trig Polarity                                      | TRIG2 must be enabled. When only one is enabled, this bit will be ignored.  0 sets the falling edge active |  |

| D10  | TIL TIIG FOIGILLY                                      | 1 sets the rising edge active.                                                                             |  |

|      |                                                        | P <sub>on</sub> state = $0$                                                                                |  |

| D9   | Software Trigger                                       | 1 = Write a 1 to trigger command execution                                                                 |  |

|      | 3011,1410 1115501                                      | 0 = Write a 0 to halt command execution                                                                    |  |

|      |                                                        | $P_{\text{on}}$ state = 0                                                                                  |  |

| D8   | Unused                                                 | Data written to this bit have no effect and always read back as 1.                                         |  |

| D7-0 | Software Trigger                                       | Sets the TTLTRIG line or lines, which are configured as inputs, and will                                   |  |

|      |                                                        | trigger the VT1802 to execute command from user. D7 corresponds to                                         |  |

|      |                                                        | TTLTRIG7, D6 to TTLTRIG6, and D0 to TTLTRIG0. Setting a bit to a                                           |  |

|      |                                                        | 1 enables the trigger line, setting a bit to 0 disables the corresponding line.                            |  |

|      |                                                        | All enabled TTLTRIG lines are OR'd together to allow more than one                                         |  |

|      |                                                        | TTLTRIG line to cause a Command Execution Trigger event to occur. All                                      |  |

|      |                                                        | bits are set to 0 when the module receives either a soft or a hard reset.                                  |  |

|      |                                                        | Note: This is different from the setup of register 0x34.                                                   |  |

|      |                                                        | riote. This is unferent from the setup of register vas4.                                                   |  |

| NOTE | The priority of triggering is as following: EXT TRIG1, EXT TRIG2, TTLTRIG0-7, and SOFTWARE. If all or many triggers are enabled, the highest priority will take precedent. The rest |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | will be ignored. TTLTRIG0-7 will be edge triggering only.                                                                                                                           |

|      | The trigger will only affects the following A24/A32 output commands: Channel Output Enable, and Channel Output Level Select.                                                        |

|      | All other A24/A32 commands and A16 will not be affected.                                                                                                                            |

| Trace RAM Restart High Register (0x28) — Read & Write |        |                                                                                                                                              |

|-------------------------------------------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------|

| D15 - D4                                              | Unused | Data written to these bits have no effect and always read back as 1.                                                                         |

| D3 - D0                                               |        | Sets the four most significant bits of the starting address of the Trace RAM, allowing the available RAM to be divided into multiple traces. |

| Trace RAM Restart Low Register (0x2A) — Read & Write |                                                                              |

|------------------------------------------------------|------------------------------------------------------------------------------|

| D15 - D0                                             | Sets the 16 least significant bits of the starting address of the Trace RAM, |

|                                                      | allowing the available RAM to be divided into multiple traces.               |

| Trace RAM End High Register (0x2C) — Read & Write |        |                                                                                                                                            |

|---------------------------------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------|

| D15 - D4                                          | Unused | Data written to these bits have no effect and always read back as 1.                                                                       |

| D3 - D0                                           |        | Sets the four most significant bits of the ending address of the Trace RAM, allowing the available RAM to be divided into multiple traces. |